# University of Western Macedonia

THESIS WORK

# Design and Implementation of a Soft Processor with a Custom FPU Addition

Author: Angelos-Eystathios Ntasios Supervisor: Minas Dasygenis

Department of Informatics and telecommunications

July 7, 2014

# **Declaration of Authorship**

I, Angelos-Eystathios Ntasios, declare that this thesis titled, "Design, Implementation and Verification of a Soft Processor with FPU Support" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

"I would like to thank my family for their support during my academic years. I would also like to express my gratitude for my supervising professor, Dr. Minas Dasygenis, without whom I would not be able to fulfil this thesis."

Angelos Ntasios

# Abstract

The ever growing need for flexibility and low production cost in hardware implementations, has led to a wider use of reprogrammable and reconfigurable hardware such as PLDs and FPGAs, which can be programmed with hardware description languages. Using reconfigurable hardware provides the option to customize existing soft-cores and soft processors in order to adapt to different design requirements.

In this thesis, an implementation of a processor based on the PLX 1.1 instruction set is presented. Since the processor is intended for multimedia data processing, it is necessary to include a floating point arithmetic unit. All the required steps that had to be taken in order to embed a floating point unit in the processor are described in detail. The whole design and implementation process of the soft core microprocessor as well as the FPU are presented, along with the customization by embedding the double precision FPU. All the stages of the work are accompanied by simulation results and FPGA implementation metrics.

# Περίληψη

Η ολοένα και αυξανόμενη ανάγκη για ευελιξία και χαμηλό κόστος παραγωγής σε υλοποιήσεις υλικού, οδήγησε σε μία ευρύτερη χρήση επαναπρογραμμαζιζόμενου και επαναδιαμορφούμενου εξοπλισμού, όπως FPGAs και PLDs, τα οποία μπορούν να προγραμματιστούν με γλώσσες περιγραφής υλικού. Η χρήση του επαναπρογραμματιζόμενου υλικού προσφέρει την επιλογή της προσαρμογής ήδη υπαρχόντων επεξεργαστών έτσι ώστε να προσαρμοτούν σε διαφορετικές σχεδιαστικές ανάγκες.

Σε αυτή την πτυχιαχή, παρουσιάζεται μία υλοποίηση ενός επεξεργαστή που βασίζεται στο σύνολο εντολών PLX 1.1 . Από τη στιγμή που ο επεξεργαστής προορίζεται για επεξεργασία δεδομένων πολυμέσων , είναι αναγχαίο να περιλαμβάνει χαι μονάδα επεξεργασίας αριθμών χινητής υποδιαστολής. Όλα τα απαραίτητα βήματα που έπρεπε να παρθούν έτσι ώστε να προσαρμόσουμε μία τέτοια μονάδα περιγράφονται λεπτομερώς. Η όλη σχεδίαση χαι υλοποίηση του επεξεργαστή χαι της μονάδας επεξεργασίας αριθμών χινητής υποδιαστολής. Όλα τα απαραίτητα βήματα που έπρεπε να παρθούν έτσι ώστε να προσαρμόσουμε μία τέτοια μονάδα περιγράφονται λεπτομερώς. Η όλη σχεδίαση χαι υλοποίηση του επεξεργαστή χαι της μονάδας επεξεργασίας αριθμών χινητής υποδιαστολής παρουσιαζονται, μαζί με την διαδιχασία προσαρμογής του επεξεργαστή έτσι ώστε να μπορέσει να λειτουργήσει με τη νέα μονάδα. Όλα τα στάδια της εργασίας συνοδεύονται με αποτελέσματα προσομοίωσης χαι με στατιστιχά από την υλοποίηση σε FPGA.

# Contents

| D  | eclara | ation o       | of Authorship                                  | i    |

|----|--------|---------------|------------------------------------------------|------|

| A  | bstra  | $\mathbf{ct}$ |                                                | iii  |

| A  | bstra  | ct gre        | ek                                             | iv   |

| Li | ist of | Figur         | es                                             | viii |

| Li | ist of | Table         | S                                              | x    |

| A  | bbrev  | viation       | IS                                             | xi   |

| 1  | Intr   | oducti        | ion                                            | 1    |

|    | 1.1    | Embe          | dded Systems                                   | 1    |

|    | 1.2    | Intelle       | ectual Property Cores                          | 3    |

|    | 1.3    | Soft M        | ficroprocessors                                | 4    |

|    |        | 1.3.1         | The Picoblaze Soft Microprocessor              | 5    |

|    |        | 1.3.2         | The Microblaze Soft Microprocessor             | 5    |

|    |        | 1.3.3         | The Xtensa Microprocessors                     | 6    |

|    |        | 1.3.4         | LEON Microprocessor                            | 6    |

|    |        | 1.3.5         | The OpenRISC Microprocessor                    | 7    |

|    | 1.4    | Floati        | ng point arithmetic                            | 7    |

|    |        | 1.4.1         | Trade offs between range and precision         | 9    |

|    |        | 1.4.2         | The floating point representation              | 9    |

|    |        | 1.4.3         | The IEEE 754 standard                          | 10   |

|    |        | 1.4.4         | Basic IEEE 754 formats                         | 11   |

|    | 1.5    | The I         | EEE 754 double precision floating point format | 11   |

|    |        | 1.5.1         | The sign bit                                   | 11   |

|    |        | 1.5.2         | The exponent                                   | 12   |

|    |        | 1.5.3         | The significand                                | 12   |

|    |        | 1.5.4         | Floating point normalization                   | 12   |

|    | 1.6    | The g         | oals of the thesis                             | 13   |

|    | 1.7    | The F         | ollowing work structure                        | 14   |

| 2  |        | proce         |                                                | 15   |

|    | 2.1    | Archit        | tecture Highlights                             | 15   |

|   |     | 2.1.1   | Datapath Size                                                                                                                          | 3 |

|---|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 2.1.2   | Subword Parallelism                                                                                                                    | 3 |

|   |     | 2.1.3   | Predication                                                                                                                            | 7 |

|   | 2.2 | Proces  | sor Implementation                                                                                                                     | 3 |

|   | 2.3 | The fit | $rst pipeline stage \dots \dots$ | 3 |

|   |     | 2.3.1   | The Program Counter                                                                                                                    | 3 |

|   |     | 2.3.2   | Program Counter Metric Statistics                                                                                                      |   |

|   |     | 2.3.3   | The Instruction Memory                                                                                                                 | ) |

|   |     | 2.3.4   | The data multiplexers                                                                                                                  | ) |

|   |     | 2.3.5   | The stage 1 data flow                                                                                                                  |   |

|   | 2.4 | The se  | $\infty$ cond pipeline stage $\ldots \ldots 21$                  |   |

|   | 2.5 |         | ird pipeline stage $\ldots \ldots 22$              |   |

|   |     | 2.5.1   | The Arithmetic Logic Unit(ALU)                                                                                                         |   |

|   |     | 2.5.2   | The Multiplier                                                                                                                         |   |

|   |     | 2.5.3   | The Mix Unit                                                                                                                           |   |

|   |     | 2.5.4   | The Shifter Unit                                                                                                                       |   |

|   |     | 2.5.5   | Predicate File, Sign Extension Unit and multiplexers                                                                                   |   |

|   | 2.6 | The fo  | $\operatorname{urth}$ Pipeline                                                                                                         |   |

|   | 2.7 |         | ifth Pipeline Stage                                                                                                                    |   |

|   |     | 2.7.1   | The register Input Unit                                                                                                                |   |

|   | 2.8 | The co  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                   |   |

|   |     | 2.8.1   | The operation decoder                                                                                                                  |   |

|   |     | 2.8.2   | The stall unit                                                                                                                         |   |

|   |     | 2.8.3   | The Flag Unit                                                                                                                          |   |

|   | 2.9 | The p   | cocessor top module                                                                                                                    |   |

|   |     |         | ls and data corruption                                                                                                                 |   |

|   |     |         | Read after write hazard                                                                                                                |   |

|   |     |         | Branch Hazards                                                                                                                         |   |

|   |     |         | Structural Hazards                                                                                                                     |   |

|   |     |         | Pipeline bubbling                                                                                                                      |   |

|   |     |         | Register Forwading                                                                                                                     |   |

|   |     |         |                                                                                                                                        |   |

| 3 | The | Float   | ing Point Unit(FPU) 37                                                                                                                 | 7 |

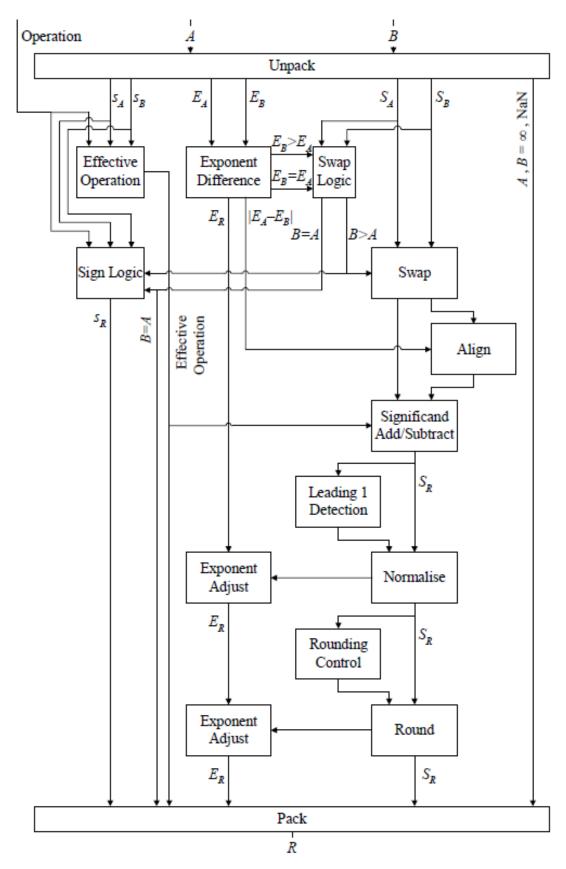

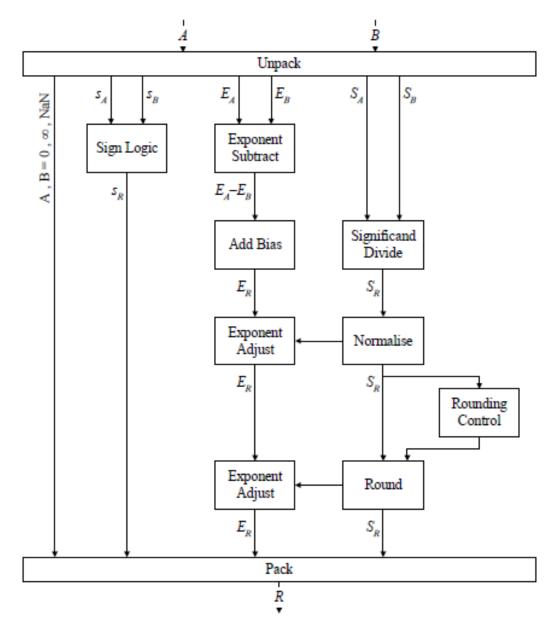

|   | 3.1 | Floati  | ng point addition-subtraction $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 38$                                      | 3 |

|   |     | 3.1.1   | FPU Adder testbench 39                                                                                                                 | ) |

|   | 3.2 | Floatin | ng point multiplication 41                                                                                                             | 1 |

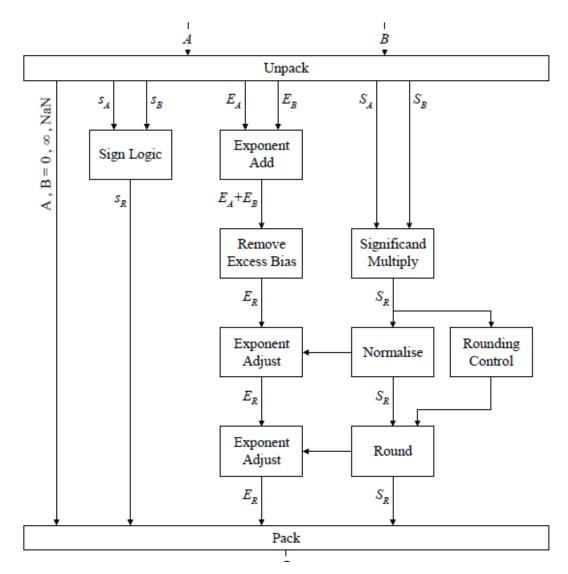

|   | 3.3 | Floati  | ng point division $\ldots \ldots 42$                      | 2 |

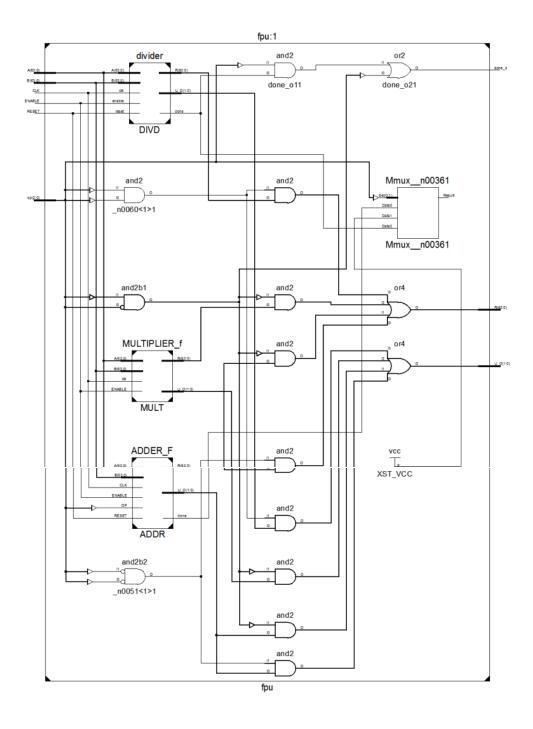

|   | 3.4 | The F   | PU Top Module                                                                                                                          | 1 |

|   |     | ъ       |                                                                                                                                        | ` |

| 4 |     |         | essor Customization 48                                                                                                                 |   |

|   | 4.1 | · · ·   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                   |   |

|   | 4.2 |         | ustomization                                                                                                                           |   |

|   | 4.3 |         | g and stalling                                                                                                                         |   |

|   | 4.4 |         | sor Testing                                                                                                                            |   |

|   |     | 4.4.1   | Data Synchronization   51                                                                                                              |   |

|   |     | 4.4.2   | Execution Testing                                                                                                                      | 5 |

| 5  | Too                      | ls Utilized                        | <b>56</b> |  |  |  |  |  |

|----|--------------------------|------------------------------------|-----------|--|--|--|--|--|

|    | 5.1                      | VHDL                               | 56        |  |  |  |  |  |

|    |                          | 5.1.1 The IEEE standard            | 57        |  |  |  |  |  |

|    |                          | 5.1.2 Advantages                   | 58        |  |  |  |  |  |

|    | 5.2                      | FPGAs                              | 58        |  |  |  |  |  |

|    |                          | 5.2.1 History                      | 60        |  |  |  |  |  |

|    |                          | 5.2.2 Modern developments          | 61        |  |  |  |  |  |

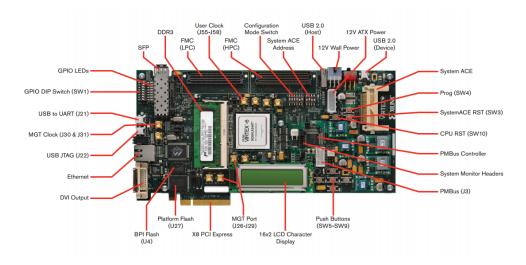

|    | 5.3                      | The Xilinx Virtex ML605            | 62        |  |  |  |  |  |

|    | 5.4                      | Xilinx ISE                         | 63        |  |  |  |  |  |

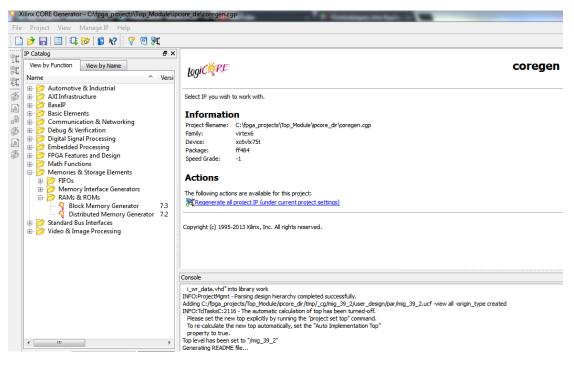

|    |                          | 5.4.1 The CORE Generator           | 64        |  |  |  |  |  |

|    | 5.5                      | Modelsim Simulation Program        | 67        |  |  |  |  |  |

| 6  | Cor                      | clusions                           | 68        |  |  |  |  |  |

|    | 6.1                      | Acknowledgements and Compromises   | 68        |  |  |  |  |  |

|    | 6.2                      | Future Work                        | 69        |  |  |  |  |  |

|    |                          |                                    |           |  |  |  |  |  |

| A  | RTI                      | schematics                         | 70        |  |  |  |  |  |

| в  | PL                       | X 1.1 Instruction Set Architecture | 78        |  |  |  |  |  |

| С  | C Segments of Code 80    |                                    |           |  |  |  |  |  |

| D  | D Module control signals |                                    |           |  |  |  |  |  |

|    |                          |                                    |           |  |  |  |  |  |

|    |                          |                                    | ~ ~       |  |  |  |  |  |

| Bi | bliog                    | raphy                              | 89        |  |  |  |  |  |

# List of Figures

| 1.1        | Embedded Systems market share              | 2               |

|------------|--------------------------------------------|-----------------|

| 1.2        | The double precision floating point format | .1              |

| 2.1        | Addition between the whole 64bit words     | 6               |

| 2.1<br>2.2 |                                            | 17              |

| 2.2<br>2.3 |                                            | 17              |

| 2.3<br>2.4 |                                            | 17              |

| 2.4<br>2.5 |                                            | 9               |

| 2.6        |                                            | 22              |

| 2.0<br>2.7 |                                            | 22              |

| 2.1        | 0 1                                        | 25              |

| 2.0<br>2.9 | *                                          | 25              |

|            |                                            | 25              |

|            | 1                                          | 26              |

|            |                                            | 26<br>26        |

|            | 1                                          | $\frac{10}{27}$ |

|            |                                            | 27<br>27        |

|            |                                            | 27<br>80        |

| 2.10       | The "jump" instruction decoding            | 90              |

| 3.1        | The .bat program                           | 10              |

| 3.2        |                                            | 10              |

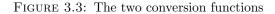

| 3.3        | The two conversion functions               | 11              |

| 3.4        |                                            | 13              |

| 3.5        |                                            | 15              |

| 3.6        |                                            | 15              |

|            |                                            |                 |

| 4.1        | 0 11                                       | 50              |

| 4.2        | 0 11                                       | 52              |

| 4.3        | 1 1 0                                      | 52              |

| 4.4        |                                            | 52              |

| 4.5        | The "and" machine code                     |                 |

| 4.6        | The processor initialization process       | 53              |

| 4.7        |                                            | 54              |

| 4.8        | The register file values                   | 55              |

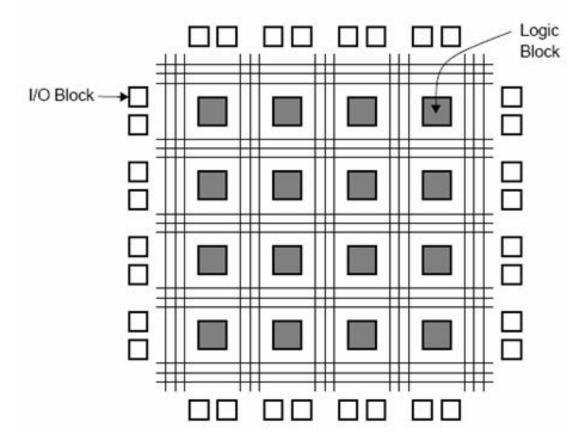

| 5.1        | FPGA block array                           | 59              |

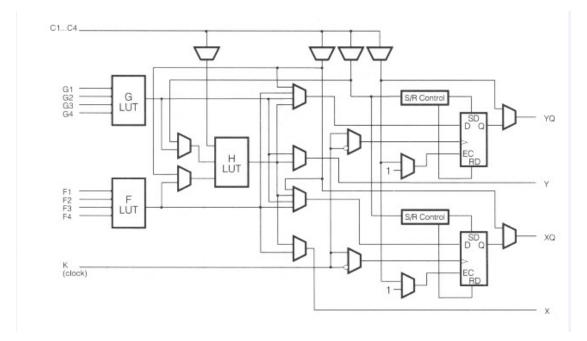

| 5.2        |                                            | 50              |

| 5.3        |                                            | 52              |

| 5.3        |                                            | 35              |

| 0.1        | Diota monory Schorator                     | .0              |

| 5.5 | The instruction memory                | 65 |

|-----|---------------------------------------|----|

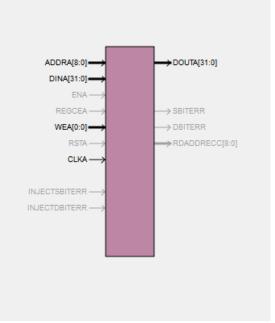

| 5.6 | The instruction memory VHDL interface | 65 |

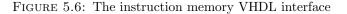

| 5.7 | The data memory                       | 66 |

| 5.8 | The data memory VHDL interface        | 66 |

| A.1 | The CPU RTL schematic                 | 71 |

| A.2 | The PC RTL schematic                  | 72 |

| A.3 | The ALU adder RTL Schematic           | 72 |

| A.4 | The control RTL Schematic             | 73 |

| A.5 | The FPU adder                         | 74 |

| A.6 | The FPU multiplier                    | 75 |

| A.7 | The FPU divider                       | 76 |

| A.8 | The FPU RTL schematic                 | 77 |

| C.1 | The FPU instruction signals           | 83 |

| C.2 | The RTL mirror design                 | 84 |

# List of Tables

| 1.1  | The IEEE 754 floating point format                 | 11 |

|------|----------------------------------------------------|----|

| 2.1  | Device Utilization Summary for the Program Counter | 19 |

| 2.2  | The Instruction Memory Ports                       | 20 |

| 2.3  | The program counter ports                          | 20 |

| 2.4  | The Register File Ports                            | 22 |

| 2.5  | The ALU Ports                                      | 23 |

| 2.6  | The multiplier ports                               | 25 |

| 2.7  | The Mix Unit ports                                 | 27 |

| 2.8  | The Shifter Unit ports                             | 28 |

| 2.9  | The OP Decoder Unit ports                          | 31 |

| 2.10 | The Stall Unit ports                               | 31 |

| 2.11 | The Control Unit ports                             | 32 |

| 2.12 | The Flag Unit ports                                | 33 |

| 2.13 | Read after write hazard example                    | 34 |

|      | Branch Hazard example                              | 35 |

| 2.15 | The Bypassing unit                                 | 36 |

| 3.1  | Device Utilization Summary for the FPU adder       | 40 |

| 3.2  | Device Utilization Summary for the FPU multiplier  | 42 |

| 3.3  | Device Utilization Summary for the FPU Divider     | 43 |

| 3.4  | Detailed device utilization summary for FPU        | 47 |

| 5.1  | std_logic values                                   | 57 |

| B.1  | Main Instructions and Mnemonics                    | 79 |

| D.1  | ALU control signals                                | 86 |

| D.2  | FPU Control Signals                                | 87 |

| D.3  | Shifter Control Signals                            | 87 |

| D.4  | Mix Unit Control Signals                           | 88 |

| D.5  | Multiplier Control Signals                         | 88 |

# Abbreviations

| $\mathbf{ALU}$ | Arithmetic Logic Unit                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------|

| $\mathbf{FPU}$ | Floating Point arithmetic Unit                                                                                     |

| FPGA           | ${\bf F} {\rm ield} \ {\bf P} {\rm rogrammable} \ {\bf G} {\rm ate} \ {\bf A} {\rm rray}$                          |

| HDL            | Hardware <b>D</b> escription Language                                                                              |

| ISA            | Instruction Set Architecture                                                                                       |

| $\mathbf{LSB}$ | $\mathbf{L} \mathbf{east} \ \mathbf{S} \mathbf{ignificant} \ \mathbf{B} \mathbf{it}$                               |

| MSB            | $\mathbf{M}$ ost $\mathbf{S}$ ignificant $\mathbf{B}$ it                                                           |

| $\mathbf{MHz}$ | $\mathbf{M}$ ega $\mathbf{H}$ eartz                                                                                |

| $\mathbf{PC}$  | $\mathbf{P} \mathrm{rogram} \ \mathbf{C} \mathrm{ounter}$                                                          |

| PLD            | $\mathbf{P} \mathrm{rogrammable} \ \mathbf{L} \mathrm{ogic} \ \mathbf{D} \mathrm{evice}$                           |

| PROM           | $\mathbf{P} \mathrm{rogrammable} \ \mathbf{R} \mathrm{ead} \ \mathbf{O} \mathrm{nly} \ \mathbf{M} \mathrm{emmory}$ |

| VLSI           | $\mathbf{V}\mathrm{ery}\ \mathbf{L}\mathrm{arge}\ \mathbf{S}\mathrm{cale}\ \mathbf{I}\mathrm{n}\mathrm{tegration}$ |

# Chapter 1

# Introduction

The modern trend in digital circuits and modern data processing, is gradually moving away from inflexible and big circuits such as desktop computer processors and is rapidly turning to more compact, adaptable and cheaper implementations. The field of embedded systems focuses in the construction of a computer system with a dedicated function, which is a crucial component of a larger installment, i.e. it is embedded within a larger system[1]. Usually these systems are in the form of micro-controllers which are processors along with all the required peripheral units, such as memory and external chips, already installed.

## 1.1 Embedded Systems

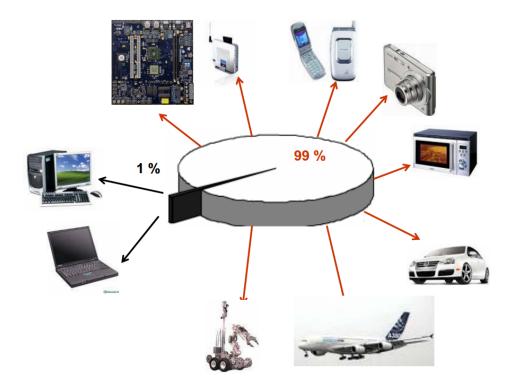

The key factor in embedded systems is their flexibility. Engineers can adapt the design very easily in order to meet certain requirements. These requirements can come in the form of area or power restrictions. Since these installments are often used in areas where the environment places a lot of restrictions, these easily adjustable systems are the go-to choice. As it is clearly evident the utilization spectrum is vast, ranging from cars and household equipment to satellites and space shuttles<sup>[2]</sup> Figure 1.1.

The embedded systems design requires fast system prototyping to validate the feasibility of various implementations and to guide toward the optimal selection. In this context, almost every embedded system engineer has at his arsenal one or more re-programmable FPGA hardware circuits. Re-programmable hardware is a term used to describe a

FIGURE 1.1: Embedded Systems market share

certain class of circuits. These circuits do not implement any specific function, but they have the potential to implement any hardware block, according to size constrains. They can be described as vast arrays of circuit blocks, each capable of functioning in various ways. By providing a specific bitstream configuration, the complete array can operate as the desired circuit e.g. processor, signal processing unit and many others. In fact there is almost no limit as to what can be implemented on these devices. Compared to the application specific integrated circuits (ASICs), they are more flexible, providing lower engineering cost, reduced development time, reduced debugging time and lower implementation risk .

The usage spectrum of FPGAs is mainly focused in areas where flexibility, low cost and rapid prototyping is mandatory. Such examples vary from radio-astronomy and particle physics to chip multiprocessor emulation and derivative pricing. All those fields have a common factor, which is the dynamic environment and alternating circumstances. It is clear that in such situations adapting, combining and incorporating IP-cores to large scale projects is mandatory.

## **1.2 Intellectual Property Cores**

With the advancement of the embedded systems market, the complexity of many designs has increased since an even wider variety of peripherals and components had to be supported. FPGAs play a major role in this advancement since the flexibility they offer allows the engineer to constantly adapt and improve his designs in order fit to different circumstances. Many modules designed and created in HDLs , are often created for a similar purpose. The ease of use offered by software allows users to easily share and even sell their work, in this case software described hardware. This gave rise to the IP-core market.

IP-cores are modules written in a hardware description language implementing a certain circuit. They can be reused and acquired either commercially or free of charge and can be used as an embedded feature in another design. The increasing complexity of the designs has rendered the usage of IP-cores a viable alternative[3]. One can simply acquire an IP-core and use it at will in his work. For example one can buy a random number generator and use it as is, in an implementation for network security. The advantages of using IP-cores are huge, as they are a solid answer to the problem of time-to-market reduction, which requires the fastest possible design and creation of a project. This is achieved because by using a preprogrammed and pretested module, there is no need of designing and debugging.

IP-cores in the electronic design industry have had a profound impact on the design of systems on a chip. By licensing a design multiple times, an IP core licensor spreads the cost of development among multiple chip makers. IP cores for standard processors, interfaces, and internal functions have enabled chip makers to put more of their resources into developing the differentiating features of their chips. As a result, chip makers have developed innovations more quickly.

The licensing and use of IP-cores in chip design came into common practice in the 1990s. There were many licensors and also many foundries competing on the market. Today, the most widely licensed IP-cores are from Synopsys, Imagination Technology, Cadence Design and ARM Holdings[4].

Typically IP-cores are offered as Soft cores or Hard cores. Soft cores are offered as synthesizable RTL designs, usually in a HDL such as Verilog or VHDL. IP cores are also sometimes offered as generic gate-level netlists. The netlist is a boolean-algebra representation of the IP's logical function implemented as generic gates or process specific standard cells. An IP core implemented as generic gates is portable to any process technology. A gate-level netlist is analogous to an assembly-code listing in the field of computer programming. A netlist gives the IP core vendor reasonable protection against reverse engineering. Both netlist and synthesizable cores are called "soft cores", as both allow a synthesis, placement and route (SPR) design flow. Hard cores on the other hand are offered by their physical low-level description, thus making them more predictable in terms of timing performance and area utilization.Such cores, whether analog or digital, are called "hard cores" (or hard macros), because the core's application function cannot be meaningfully modified by chip designers. Transistor layouts must obey the target foundry's process design rules, and hence, hard cores delivered for one foundry's process cannot be easily ported to a different process or foundry.

## **1.3** Soft Microprocessors

As mentioned earlier, embedded systems are a vital part of our everyday interaction with technology. These systems often have special restrictions, mainly in power consumption and cost. Usually these systems contain embedded processors either in the form of micro-controllers or soft processors. In addition to these constraints, many embedded system developers are faced with tight timeto- market deadlines. Hence, the hardware/software codesign methodology is often used to design embedded systems in order to help reduce the amount of time spent on development and debugging. Soft microprocessor is a microprocessor solely implemented using logic synthesis and HDLs. They can be implemented in varisous reprogrammable semiconductor devices such as FPGAs, PLDs, ASICs. The use of soft-core processors holds many advantages for the designer of an embedded system. First, soft-core processors are flexible and can be customized for a specific application with relative ease. Second, since soft-core processors are technology independent and can be synthesized for any given target ASIC or FPGA technology, they are therefore more immune to becoming obsolete when compared with circuit or logic level descriptions of a processor. Finally, since a softcore processor's architecture and behavior are described at a higher abstraction level using an HDL, it becomes much easier to understand the overall design.<sup>[3]</sup>

#### 1.3.1 The Picoblaze Soft Microprocessor

Picoblaze is a soft microprocessor offered by Xilinx. It is based on an 8-bit RISC architecture and can reach speeds up to 100 MIPS on the Virtex 4 FPGA's family. The processor has an 8-bit address and data port for access to a wide range of peripherals. The license of the cores allows their free use, albeit only on Xilinx devices, and they come with development tools. The PicoBlaze microcontroller core is totally embedded within the target FPGA and requires no external resources. The basic functionality is easily extended and enhanced by connecting additional FPGA logic to the microcontroller's input and output ports. the PicoBlaze peripheral set can be customized to meet the specific features, function, and cost requirements of the target application. Because the PicoBlaze microcontroller is delivered as synthesizable VHDL source code, the core is future-proof and can be migrated to future FPGA architectures, effectively eliminating product obsolescence fears. Being integrated within the FPGA, the processor reduces board space, design cost, and inventory[5].

#### 1.3.2 The Microblaze Soft Microprocessor

MicroBlaze is a 32-bit RISC Harvard architecture soft processor core which is created and offered for free by Xilinx. They key feature of this processor is its high customizability and flexibility. MicroBlaze contains over 70 user-configurable options, enabling virtually any processor use case from a very small footprint state machine or microcontroller to a high performance compute-intensive microrocessor-based system running Linux, operating in either 3-stage pipeline mode to optimize size, or 5-stage pipeline mode to optimize speed. These parameters include an optional IEEE-754 compatible single precision FPU, a hardware divider, a barrel shifter, data and instruction caches, exception handling capabilities, hardware debug logic and many more[3]. Both Picoblaze and Microblaze come freely with the Embedded Development Kit (EDK) which is offered from Xilinx. Both of these processors are small and focus mainly in flexibility and low power consumption.

#### **1.3.3** The Xtensa Microprocessors

Tensilica's Xtensa technology provides a variety of soft processors for embedded systems. This processor family is focused mainly in flexibility and customizability. A series of options is offered from which to choose the ones that are needed. One important key feature is that they are extensible in that custom instructions and custom units can be added to the processor. This feature is supported by a custom Verilog language created by Tensilica, the Tensilica Instruction Extension, which is used to describe the new instructions[3]. An automated HDL generator is also available for this processor, which creates HDL modules of the customized processor.

#### 1.3.4 LEON Microprocessor

LEON is a 32-bit CPU microprocessor core, based on the SPARC-V8 RISC architecture and instruction set. It was originally designed by the European Space Research and Technology Centre (ESTEC), part of the European Space Agency (ESA), and after that by Gaisler Research. It is described in synthesizable VHDL. LEON has a dual license model: An LGPL/GPL FLOSS license that can be used without licensing fee, or a proprietary license that can be purchased for integration in a proprietary product. The core is configurable through VHDL generics, and is used in system-on-a-chip (SOC) designs both in research and commercial settings.

The LEON project was started by the European Space Agency (ESA) in late 1997 to study and develop a high-performance processor to be used in European space projects. The objectives for the project were to provide an open, portable and non-proprietary processor design, capable to meet future requirements for performance, software compatibility and low system cost. Another objective was to be able to manufacture in a Single event upset (SEU) sensitive semiconductor process. To maintain correct operation in the presence of SEUs, extensive error detection and error handling functions were needed. The goals have been to detect and tolerate one error in any register without software intervention, and to suppress effects from Single Event Transient (SET) errors in combinational logic.

The LEON family includes the first LEON1 VHSIC Hardware Description Language (VHDL) design that was used in the LEONExpress test chip developed in  $0.25 \ \mu m$

technology to prove the fault-tolerance concept. The second LEON2 VHDL design was used in the processor device AT697 from Atmel (F) and various system-on-chip devices. These two LEON implementations were developed by ESA. Gaisler Research, now Aeroflex Gaisler, developed the third LEON3 design and has announced the availability of the fourth generation LEON, the LEON4 processor[6].

#### 1.3.5 The OpenRISC Microprocessor

OpenRISC is the original flagship project of the OpenCores community. This project aims to develop a series of general purpose open source RISC CPU architectures. The first (and currently only) architectural description is for the OpenRISC 1000, describing a family of 32 and 64-bit processors with optional floating point and vector processing support.

A team from OpenCores provided the first implementation, the OpenRISC 1200, written in the Verilog hardware description language. The hardware design was released under the GNU Lesser General Public License (LGPL), while the models and firmware were released under the GNU General Public License (GPL). A reference SoC implementation based on the OpenRISC 1200 was developed, known as ORPSoC (the OpenRISC Reference Platform System-on-Chip).

The instruction set is a reasonably simple MIPS-like traditional RISC using a 3-operand load-store architecture, with 16 or 32 general-purpose registers and a fixed 32-bit instruction length. The instruction set is mostly identical between the 32 and 64 bit versions of the specification, the main difference being the register width (32 or 64 bits) and pagetable layout. The OpenRISC specification includes all features common to modern desktop/server processors: a supervisor mode and virtual memory system, optional read, write and execute control for memory pages, and instructions for synchronization and interrupt handling between multiple processors[7].

## **1.4** Floating point arithmetic

In computer science the programs or the circuits that are implemented to deal wih calculations, always deal with natural numbers. Since the fundamental basis of the calculations is the bit, all other numbers such as rational, fractions and irrational are represented, and often represented by an approximation, by real numbers. As it is clear a standard had to be established in order to represent these numbers so as to be used in computer science. The term floating point refers to the fact that a number's radix point in computers, can "float". That is, it can be placed anywhere relative to the significant digits of the number. This position is indicated as the exponent component in the internal representation, and floating point can thus be thought of as a computer realization of scientific notation. All floating point numbers are represented with the following formula:

$$Significant Digits * base^{exponent}$$

(1.1)

The numbers are, in general, represented approximately to a fixed number of significant digits (the significand) and scaled using an exponent. The base for the scaling is normally 2, 10 or 16. The idea of floating-point representation over intrinsically integer fixed-point numbers, which consist purely of significand, is that expanding it with the exponent component achieves greater range. For instance, to represent large values, e.g. distances between galaxies, there is no need to keep all 39 decimal places down to femtometreresolution (employed in particle physics). Assuming that the best resolution is in light years, only the 9 most significant decimal digits matter, whereas the remaining 30 digits carry pure noise, and thus can be safely dropped. This represents a savings of 100 bits of computer data storage. Instead of these 100 bits, much fewer are used to represent the scale (the exponent), e.g. 8 bits or 2 decimal digits. Given that one number can encode both astronomic and subatomic distances with the same nine digits of accuracy, but because a 9-digit number is 100 times less accurate than the 11 digits reserved for scale, this is considered a trade-off exchanging range for precision. The example of using scaling to extend the dynamic range reveals another contrast with fixed-point numbers: Floating-point values are not uniformly spaced. Small values, close to zero, can be represented with much higher resolution (e.g. one femtometre) than large ones because a greater scale (e.g. light years) must be selected for encoding significantly larger values.[1] That is, floating-point numbers cannot represent point coordinates with atomic accuracy at galactic distances, only close to the origin.

#### 1.4.1 Trade offs between range and precision

It is crucial to point out that by using the floating point representation we have not managed to represent more numbers. If for example we use a 64 bit floating point we can still represent only  $2^{64}$  distinct numbers. However we have spread those distinct representations to a wider range.

There will always be a compromise between the range and the desired precision. Since there is only a given number of representation bits, by increasing the number of the exponent bit we achieve a greater range however there is a significand loss of precision as to which numbers in this range we can represent. Likewise by increasing the number of bits in the significand part we increase the precision but there is a smaller range of numbers to represent[8].

#### 1.4.2 The floating point representation

A number representation specifies a way of storing a number in the form of a string of digits. There are several mechanics by which strings of digits can represent numbers. the digit string can be of any length, and the location of the radix point is indicated by placing an explicit "point" character (dot or comma) there. If the radix point is not specified then it is implicitly assumed to lie at the right end of the string. In fixed-point systems, some specific assumption is made about where the radix point is located in the string. For example, the convention could be that the string consists of 8 decimal digits with the decimal point in the middle, so that "00012345" has a value of 1.2345. In scientific notation, the given number is scaled by a power of 10 so that it lies within a certain range—typically between 1 and 10, with the radix point appearing immediately after the first digit. The scaling factor, as a power of ten, is then indicated separately at the end of the number.

The floating point representation, as shown in 1.1, consists of three parts.

• A signed string of digits of a given length, that represent the base of the number. It is usually referred to as the significand or mantissa. The length of this string determines the precision of the representation to be implemented. For example a

- A signed string of digits that represent the exponent, that modifies the magnitude of the number. The length of the string represents the range of the numbers that can be represented.

- An unsigned number which represents the base which is usually the number 2.

To derive the value of the floating-point number, one must multiply the significand by the base raised to the power of the exponent, equivalent to shifting the radix point from its implied position by a number of places equal to the value of the exponent to the right if the exponent is positive or to the left if the exponent is negative.

#### 1.4.3 The IEEE 754 standard

The most used floating point format used today is the IEEE 754. The IEEE has standardized the representation used in most today's computers with some exceptions. The technical standard was established in 1985 and defines the following:

- arithmetic formats: sets of binary and decimal floating-point data, which consist of finite numbers (including signed zeros and subnormal numbers), infinities, and special "not a number" values (NaNs)

- interchange formats: encodings (bit strings) that may be used to exchange floatingpoint data in an efficient and compact form

- rounding rules: properties to be satisfied when rounding numbers during arithmetic and conversions

- operations: arithmetic and other operations on arithmetic formats

- exception handling: indications of exceptional conditions (such as division by zero, overflow, etc.)

| sign  | exponent | significand |

|-------|----------|-------------|

| Γ     | Γ        | Ų           |

| 1 bit | 11 bits  | 52 bits     |

FIGURE 1.2: The double precision floating point format

#### 1.4.4 Basic IEEE 754 formats

The standard defines five basic formats, which differ in that each has a different length in the strings of the significand and the exponent. Two of these format refer to a decimal representation but they are not going to be described here. The three binary representations are encoded with 32, 64, 128 bits respectively.

TABLE 1.1: The IEEE 754 floating point format

| Name       | Common name         | Base | Digits  | E min  | E max  | Decimal digits | Decimal E max |

|------------|---------------------|------|---------|--------|--------|----------------|---------------|

| binary16   | Half precision      | 2    | 10+1    | -14    | +15    | 3.31           | 4.51          |

| binary32   | Single precision    | 2    | 23+1    | -126   | +127   | 7.22           | 38.23         |

| binary64   | Double precision    | 2    | 52+1    | -1022  | +1023  | 15.95          | 307.95        |

| binary128  | Quadruple precision | 2    | 112 + 1 | -16382 | +16383 | 34.02          | 4931.77       |

| decimal32  |                     | 10   | 7       | -95    | +96    | 7              | 96            |

| decimal64  |                     | 10   | 16      | -383   | +384   | 16             | 384           |

| decimal128 |                     | 10   | 34      | -6143  | +6144  | 34             |               |

## 1.5 The IEEE 754 double precision floating point format

Since in our implementation we use a double precision floating point arithmetic unit, we will explain in more details the double precision format. The double precision format uses 64 bits in total to represent floating point numbers. Figure 1.2 displays the format of the number.

#### 1.5.1 The sign bit

The first bit of the 64 bits, or the most significand bit, is used to represent the sign of the number. Zero is used to represent positive numbers and one to represent negative numbers.

#### 1.5.2 The exponent

The next 11 bits are used to represent the exponent. It is crucial to mention here that the actual value of the exponent is not the value that is stored. For E the value stored the true value of the exponent is given by equation 1.2,  $E_{bias}$  is the number 1023. In order to represent negative as well as positive numbers the number 1023 is subtracted from the number to get the real value. With 11 bits the largest number that can be represented is 2047 and the lowest 0, after the bias subtraction we get 1024 as the highest value and -1023 as the lowest that can be represented.

$$e = E - E_{bias} \tag{1.2}$$

#### 1.5.3 The significand

The significand of the floating point number is represented by a string of 52 bits. However the actual number is not just these 52 bits. The fraction f stored in these 52 bits is in the range [0-1). The significand S is calculated with the equation 1.3. A more detailed explanation of the leading '1' digit follows in the next section.

$$S = 1.f \tag{1.3}$$

#### 1.5.4 Floating point normalization

As mentioned earlier the actual bits of the significand part of the number are 53 and not 52. This happens because the MSB is always assumed to be one and therefore does not need to be stored which leads to storing area reduction. The final result of the calculation of any two floating point numbers, must have the MSB of the significand part equal to 1. However after a calculation it is often that the MSB will not be equal to 1, in which case the number must be normalised so as to change the MSB to 1. If the number is not normalized there are two possibilities, one the MSB is zero and second an overflow has occurred and a extra bit has been concatenated to the left of the significand. If the second has occurred no actual normalization has to take place regarding the significand part of the number however the exponent should be right shifted by one(A more detailed explanation is given in chapter \*\*\*\*\*\* about the Floating point implementation). If the MSB is zero then the significand must be shifted left by one and a zero must be concatenated to the right of the LSB as displayed in figure 1.4.

$$\xleftarrow{^{\rm left \ shift \ by \ one}} \underbrace{\overset{64 \ bits}{0.111010100...111}}_{}$$

$$\underbrace{\begin{array}{c} 64 \text{ bits} \\ 1.111010100...110 & \leftarrow \text{a zero has been concatenated} \end{array}}_{\text{(1.4)}$$

## 1.6 The goals of the thesis

It is crucial at this point to mention the goal of the work implemented as well as the motivation. This thesis work presents a way of designing and creating a soft processor which is based on ISA PLX 1.1[9]. Furthermore it is also important to highlight the flexibility of soft processors and for this reason, we implemented a customization on this processor by adding a custom FPU core. The whole process is described in full detail in the following chapters.

The full methodology of how to customize an IP-core and adjust it to someone's needs is presented, allowing someone by using it to create and customize his own cores. This is very important since it can save up valuable time which would be otherwise spent in an effort to figure out the most efficient way to accomplish the creation and customization of a module.

A complete implementation of a Floating Point Arithmetic Unit is also presented, providing a clear picture as to how it was implemented and tested. An existing design, specifically created to target FPGA devices, was used[10] and implemented. A testbench was also created allowing the user to verify the integrity of some features of the FPU.

## 1.7 The Following work structure

The following paper is structured as follows: Chapter 2 describes the processor implemented and its main characteristics as well as the key features and the goals behind the design. Chapter 3 describes the implementation of the FPU as well as the verification. Chapter 4 describes the processor customization in order to augment the FPU module as well as the testing of the processor. Chapter 5 describes all the necessary programming tools that were used along with the hardware. Chapter 6 is the epilogue with suggestions for improvements and acknowledged compromises of the design.

# Chapter 2

# The processor

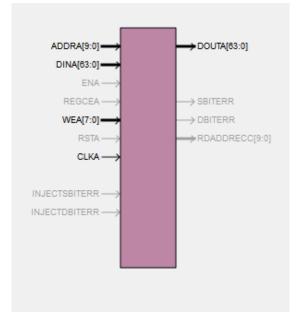

In this chapter the whole process of designing and implementing the processor that was used is explained in detail. Most of the soft processors available, are general purpose with a main focus in flexibility and an all around usability. However all of these processors are well understood and developed and there is very little room for customization. Almost all the popular softcores have a development environment that fully supports customization. As a result the processor chosen to be implemented here is based on ISA PLX 1.1[9], an instruction set developed by professor Ruby B. Lee from Princeton University. It is a small processor that supports parallel subword instructions and is intended for multimedia processing. The full instruction set encoding tables can be found here [11]. Where needed the assumed register order in the instruction encoding tables is as follows: 1) Register Rd, 2) Register Rs1, 3) Register Rs3.

## 2.1 Architecture Highlights

The instruction set is designed for RISC architecture implementation. It is optimized for high speed multimedia processing. There are two features that distinguish multimedia processors from simple general purpose processors: Large amounts of parallel subword data processing and use of low precision data[12]. Both of these features are characteristics of the PLX instruction set. The processor utilizes 32 general-integer registers numbered R0 to R31. The register size is the same as the word width and an be 32, 64 or 128 bits long. Adjusting the size does not require any changes to the instruction set.

FIGURE 2.1: Addition between the whole 64bit words

#### 2.1.1 Datapath Size

The datapath size chosen for the soft processor is 64 bits wide. The ISA itself supports 32, 64 and 128 bits datapaths, however the 64 bit wide is the silver lining among the other two[12]. Another feature that led to the decision of the 64bit wide datapath is the fact that the FPU implementation described at chapter 3 is a double precision one, hence the 64 bits. This is yet another example of the flexibility that is offered by soft core implementations; designers are free to choose the datapath and experiment with various sizes and make the best decision for their design. Smaller datapath reduces consumption and cost, while larger datapaths increase the performance. Register R0 is hardwired to 0 meaning that no changes can be made to this register and the value returned when requested will always be zero. R31 is the designated jump register used for the jump instructions.

#### 2.1.2 Subword Parallelism

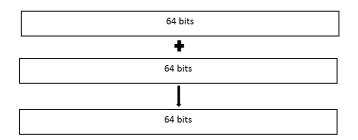

The key characteristic of the processor is the subword parallelism support. This means that certain instructions can be executed simultaneously to all the subwords of the 64bit word. The subword size can be chosen by the program and is 8, 16, 32 or 64 bit long. For example when executing the addition instruction between two words a choice can be made so as to add the two 64 bit words or add separately their subwords as displayed in figures 2.1, 2.2, 2.3, 2.4. Subword parallelism can increase the speed by up to 8 times depending on the word size chosen. However it is evident that there is a significand loss in precision when using the parallel instructions, but multimedia processing has a large margin for these kinds of precision losses.

FIGURE 2.2: Addition between the two 32bit words

| 16 bits | 16 bits | 16 bits | 16 bits |  |

|---------|---------|---------|---------|--|

| +       | +       | +       | +       |  |

| 16 bits | 16 bits | 16 bits | 16 bits |  |

| ļ       |         | ļ       | ļ       |  |

| 16 bits | 16 bits | 16 bits | 16 bits |  |

FIGURE 2.3: Addition between the four 16bit

| 8 bits |

|--------|--------|--------|--------|--------|--------|--------|--------|

| +      | +      | +      | +      | +      | +      | +      | +      |

| 8 bits |

| ļ      | ļ      | ļ      |        | ļ      | ļ      | ļ      |        |

| 8 bits |

FIGURE 2.4: Addition between the 8 8bit words

#### 2.1.3 Predication

All the instructions in PLX are predicated. This means that every instruction has a flag bit attached, if this bit is one then the instruction is executed else it is not. This results in the processor not having branch instructions or branch hazards. All of the instructions are propagated through the pipeline and those that have a zero predicate flag are simply not executed. There are eight 1-bit predicate registers, numbered P0 to P7. There are 16 of there 1byte predicate registers forming the predicate file. At any given time only one register is active which is chosen by software. P0 is hardwired to 1 meaning that all instructions assigned to this predicate register will be executed.

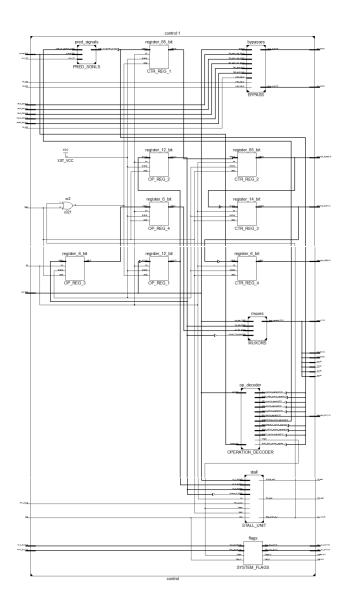

## 2.2 Processor Implementation

The main goals for the implementation were efficiency in terms of speed and area consumption. It is crucial at this point to mention that the goals set are solely for educational purposes and no actual research was done in order to determine the optimal designing goals.

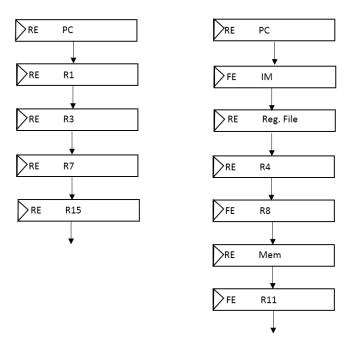

The first step is to choose the overall design method for the processor. A five stage pipelined non-superscalar design was chosen. The five stages were chosen in order to isolate time consuming components, such as the memory access and data processing. After many experiments the five stage pipeline was found to be the most ideal choice. The data and instruction memories as well as the shifting unit were the slowest components and had to be isolated. Further increase in the number of pipeline stages was unnecessary and would result in no gain, because the memory access and the shifting unit operations could not be divided further. Thus, by isolating all the data processing units, along with the shifting module, we achieved the best performance, than every other number of pipeline stages. Since the project targets an FPGA board, area was of utmost importance so the superscalar approach was ignored. Appendix A Figure A.1 displays the RTL implementation of the PLX processor, using 5 pipeline stages.

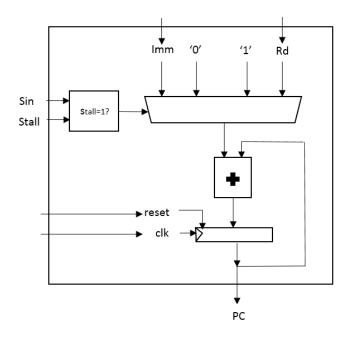

## 2.3 The first pipeline stage

The first stage of the pipeline contains the program counter and the instruction memory. The program counter is responsible for providing the proper address of the Instruction Memory, that contains the next instruction to be fetched and executed by the processor. Appendix A Figure A.2 displays the RTL schematic of the program counter.

The module has seven ports, 6 input ports and 1 output which is the value of the program counter. Table 2.3 shows the ports of the program counter module.

#### 2.3.1 The Program Counter

Depending on the instruction, the program counter increments by 1, by the value "Imm" provided by the instruction or by the value stored in the Rd register. The value 1 is the

FIGURE 2.5: PC simulation

TABLE 2.1: Device Utilization Summary for the Program Counter

| Logic Utilization           | Used | Available | Utilization |

|-----------------------------|------|-----------|-------------|

| Number of Slice Registers   | 64   | 93120     | 0%          |

| Number of slice LUTs        | 134  | 46560     | 0%          |

| Number of used LUT-FF pairs | 64   | 134       | 47%         |

| Number of bonded IOBs       | 156  | 240       | 65%         |

| Number of BUFG/BUFGCTRLs    | 1    | 32        | 3%          |

default value added to the current PC to calculate the next address of the Instruction Memory since the width of the memory is 32bits which is equal to the instruction word size. As a result there is one instruction per line stored in the memory and the program counter needs to increment by one to point to the next instruction. Some instructions require the program counter to increment by a certain value; this value can be stored either in the specified register Rd or it can be acquired directly from the instruction stored in the instruction memory (input Imm). The width size of the program counter value is 9 bits since the instruction memory size is 512 words. The value of the program counter is reset either by an external signal or if the value reaches 512.

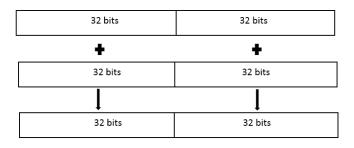

After the design of the module, it needs to be verified for proper functioning. The program "Modelsim PE student edition" was used to simulate the design and test the correct functionality. In figure 2.5 a short simulation is displayed where the counter increases for 5 cycles and in the sixth a constant value is added via the "Imm" value.

#### 2.3.2 Program Counter Metric Statistics

The maximum achieved frequency is 294.638MHz<sup>1</sup>. The size of this module is very small since it only consists of a 64bit adder, a 64bit register and 3 multiplexers. Table 2.1 shows the device utilization summary as generated by the ISE development kit. The total power consumption is 1.293Watts.

$<sup>^1{\</sup>rm The}$  device used for the implementation is the Xilinx Virtex ML605; more details provided in Chapter 6

| Name                   | $\mathbf{Type}$ | Size | Explanation                  |

|------------------------|-----------------|------|------------------------------|

| clka                   | input signal    | 1    | clock signal                 |

| wea                    | input signal    | 1    | memory initialization signal |

| $\operatorname{addra}$ | input signal    | 32   | memory address               |

| dina                   | input signal    | 32   | input data                   |

| douta                  | output signal   | 1    | output data                  |

TABLE 2.2: The Instruction Memory Ports

TABLE 2.3: The program counter ports

| Name                   | $\mathbf{Type}$ | Size | Explanation            |

|------------------------|-----------------|------|------------------------|

| Sin                    | input signal    | 2    | functionality signals  |

| Rd                     | input signal    | 64   | Rd register value      |

| Imm                    | input signal    | 23   | immediate value        |

| clk                    | input signal    | 1    | clock signal           |

| res                    | input signal    | 1    | reset signal           |

| $\operatorname{stall}$ | input signal    | 1    | stall signal           |

| $\mathbf{PC}$          | output signal   | 64   | program counter output |

#### 2.3.3 The Instruction Memory

The instruction memory used is a 512x32bits block memory as mentioned earlier. The memory is generated be the Xilinx CORE Generator System[13]. This tool provides an easy way to communicate with the on-board memory found on the FPGA used. A more thorough explanation for the tool is given in chapter 6. This module has 3 ports plus two "hidden". The 3 standard ports are a 9bit address input port, a 32bit output data port and a 1bit clock input port. The "hidden" ports are the ones used to initialize the memory, i.e. to store the program to be executed. There is a 1bit initialization signal which stalls the memory and the processor and a 32bit signal carrying one instruction per clock cycle. To initialize the memory one simply has to raise the initialization signal to high, which automatically stalls the processor, and then input the instructions one per clock cycle to subsequent addresses. The standard frequency for the memory module is 144MHz. Table 2.2 displays all the port signals of the Instruction Memory.

#### 2.3.4 The data multiplexers

Stage one of the pipeline contains two multiplexers that provide the two addresses required for the register file. Multiplexer M1 provides the address for the Rs2 or Rd register depending on the instruction. There are three possible locations in the instruction word: a) bits 12 down to 8, b) bits 17 down to 13, c) bits 22 down to 18. Multiplexer M2 provides the address for the Rs1 register and the value is either in bits 17 down to 13 or in bits 22 down to 18. Both multiplexers are controled by the control unit and their value is automatically provided.

#### 2.3.5 The stage 1 data flow

Stage one operates in one clock cycle. The program counter operates on the falling edge of the clock and provides the new value when clock has value '0'. The instruction memory operates on opposite clock cycle, i.e. rising edge of the clock. This allows the instruction memory to provide the new instruction in the same clock cycle as the program counter produces the new value, merging the two components in one stage. As soon as the clock takes the low value the program counter provides a new 64bit value. However only the 9 least significand bits are used to acquire the new instruction memory since its size is 512 words, hence 9 bits are required to encode all the addresses. The program counter produces a 64 bit value because the value needs to be used in the next stages. As soon as the instruction memory receives a new value it provides the new instruction which is driven in the control unit. The value that is fed in the control unit is the concatenation of the following bit strings: a) 28 down to 23, b) 17 down to 16, c) 7 down to 0. Bits 22 down to 0 and 31 down to 29 are driven to the multiplexers M1 and M2. The control unit provides the proper signals for this stage immediately after the new value is provided by the instruction memory.

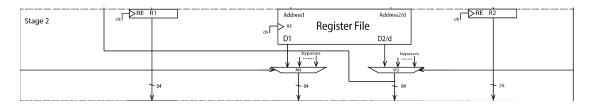

## 2.4 The second pipeline stage

The second stage contains the reading part of the register file and the two data multiplexers. The register file stores 32 64bit words. Table 2.4 displays all the ports for the register file. The reading of the data in the register file is done in the falling edge of the clock while the writing, which is done in stage 5, is done in the rising edge so as to avoid data corruption in case a read an write instruction of the same register is performed simultaneously. This stage also contains the two bypassing multiplexers M3 and M4, more details about the data bypassing in the Hazard Dealing section.

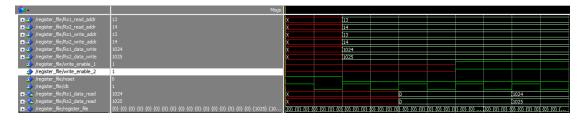

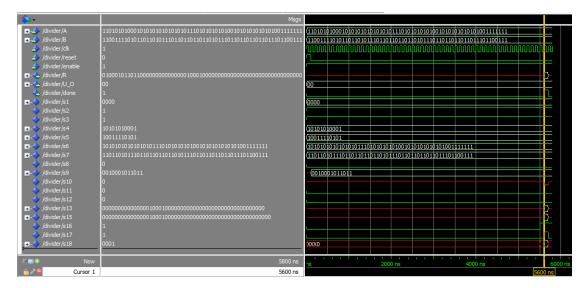

Figure 2.6 displays a short simulation of the Register File. After the module is being reset two values 1024 and 1025 are driven to the addresses 13 and 14 respectively. However

FIGURE 2.6: Register File Simulation

TABLE 2.4: The Register File Ports

| Name                                                                                | $\mathbf{Type}$                                                               | Size                         | Explanation                                                                             |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------|

| Rs1_read_addr                                                                       | input signal                                                                  | 5                            | read address                                                                            |

| $Rs2\_read\_addr$                                                                   | input signal                                                                  | 5                            | read address                                                                            |

| $Rs1_write_addr$                                                                    | input signal                                                                  | 5                            | write address                                                                           |

| $Rs2\_write\_addr$                                                                  | input signal                                                                  | 5                            | write address                                                                           |

| $Rs1_data_write$                                                                    | input signal                                                                  | 64                           | write data                                                                              |

| $Rs2_data_write$                                                                    | input signal                                                                  | 64                           | write data                                                                              |

| $write_enable_1$                                                                    | input signal                                                                  | 1                            | write enable                                                                            |

| $write\_enable_2$                                                                   | input signal                                                                  | 1                            | write enable                                                                            |

| reset                                                                               | input signal                                                                  | 1                            | reset                                                                                   |

| $\operatorname{clk}$                                                                | input signal                                                                  | 1                            | clock signal                                                                            |

| $Rs1_data_read$                                                                     | output signal                                                                 | 64                           | data read output                                                                        |

| $Rs2_data_read$                                                                     | output signal                                                                 | 64                           | data read output                                                                        |

| Rs2_data_write<br>write_enable_1<br>write_enable_2<br>reset<br>clk<br>Rs1_data_read | input signal<br>input signal<br>input signal<br>input signal<br>output signal | 64<br>1<br>1<br>1<br>1<br>64 | write data<br>write enable<br>write enable<br>reset<br>clock signal<br>data read output |

the read ports do not register any change until the write enable signals are activated. As soon as the write enable signals are activated the data read ports provide the value in the next clock cycle. The register file operates at a maximum frequency of 382,117 MHz and occupies less than 1% of the FPGA

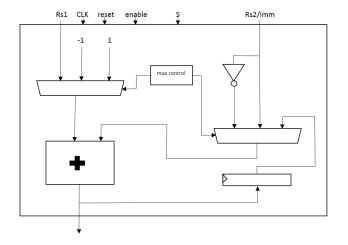

## 2.5 The third pipeline stage

The third stage of the pipeline is the data processing stage. Here all the data processing takes place and all the data processing units are contained. This stage is the most time consuming since it contains the slowest unit which is the shifter. This stage also contains the predicate file and a sign extension unit along with some multiplexers.

### 2.5.1 The Arithmetic Logic Unit(ALU)

The ALU is responsible for the basic calculations (add, subtract), the comparisons and the logic calculations. The top level design contains two components, the adder and the logic calculations module as well as some logic for the calculation of the test\_bit. Table

| Name                  | Type          | Size | Explanation             |

|-----------------------|---------------|------|-------------------------|

| Rs1                   | input signal  | 64   | Rs1 register data       |

| Rs2                   | input signal  | 64   | Rs2 register data       |

| $\mathbf{S}$          | input signal  | 1    | operation signals       |

| clk                   | input signal  | 1    | clock input             |

| enable                | input signal  | 1    | enable signal           |

| reset                 | input signal  | 1    | reset signal            |

| Rd                    | output signal | 64   | Result data             |

| $\operatorname{trap}$ | output signal | 1    | trap flag               |

| OVF                   | output signal | 8    | overflow/underflow flag |

| $T_{-}F$              | output signal | 1    | true/false flag         |

TABLE 2.5: The ALU Ports

2.5 displays the ports used by the ALU module. This unit is responsible for the results from the following instructions: Addi, And, Andem, Andi, Cmp, Cmpi, Not, Or, Ori, Padd, Paddiner, Pavg, Pemp, Pmax, Pmin, Psub, Psubavg, Psubdeer, Psubavg, Subi, Testbit, Xor, Xori.

ALU operates in one, two or three cycles depending on the operation. All the logic calculations (or, nor, xor, not, and) require one cycle. Addition is performed also in one cycle with the exception of the addincr instruction, which adds two values and increments the result by one, which is done in two cycles. Subtraction is performed in two clock cycles, since the subtraction is performed with an adder the two's compliment method is used. The value to be subtracted is first converted to its two's compliment negative equivalent, this is done using the formula 2.1 where n the two's compliment number and b the original number. In the first cycle a '1' is subtracted from the numbers' compliment and in the second cycle the addition takes place. Similarly if the number needs to be decremented by 1 the operation takes up one more clock cycle. The ALU operates at 218,627 MHz and occupies 1% of the FPGA slices.

$$n = \bar{b} - 1 \tag{2.1}$$

The actual adder of the ALU is an array of 8 1byte adders. Since the addition can be performed on a varying word size the smallest possible word size adder must be used. The basic 1byte full adder is a standard full adder with the exception of providing an extra output the carry out of the 6th half adder. This carry out is required in order to detect overflows in signed calculations. Each adder has the carry out connected to

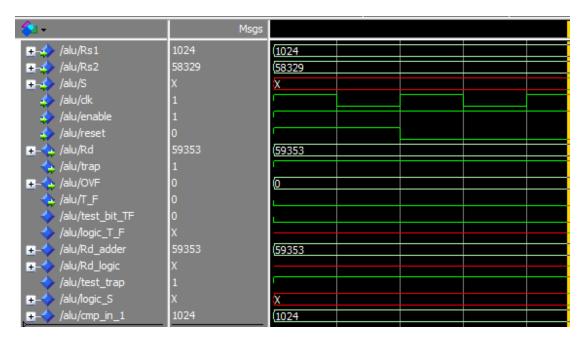

FIGURE 2.7: ALU simulating an addi operation

the next adder as well as the proper adders required when executing subword additions. For example if the addition is performed between 4 32bit size words, the fourth adders' carry out will be driven to the first adder and the 8th adder's carry out will be driven to the 5th adder as displayed in Figure 2.8 and 2.9. This carry out propagation is required only for the modular addition where the carry out is fed back to the carry in. The adder can perform signed/unsigned and modular/non-modular additions/subtractions.

The comparator performs all the basic comparisons (equality, comparison, minimum, maximum) between the two 64bit words as well as between all the subwords separately depending on the instruction.

Figure 2.7 displays an example of the simulation of the ALU. Presenting here every single instruction and subword combination is not possible, however all instructions have been simulated and verified. Appendix D provides a full list with all the components, including the ALU, and their signal encoding according to the instructions; refer to this table to set the proper signals in the simulations.

#### 2.5.2 The Multiplier

The multiplier performs all the basic multiplying instructions. It can perform signed or unsigned multiplications between 16bit size words. These words can be either the odd

FIGURE 2.8: Carry out drive between two 64 bit numbers

FIGURE 2.9: Carry out drive between four 32 bit numbers

FIGURE 2.10: Multiplier Simulation

| TABLE | 2.6: | The | multiplier | ports |

|-------|------|-----|------------|-------|

|-------|------|-----|------------|-------|

| Name         | $\mathbf{Type}$ | Size | Explanation       |

|--------------|-----------------|------|-------------------|

| Rs1          | input signal    | 64   | Rs1 register data |

| Rs2          | input signal    | 64   | Rs2 register data |

| $\mathbf{S}$ | input signal    | 7    | operation signals |

| enable       | input signal    | 1    | enable signal     |

| Rd           | output signal   | 64   | Result data       |

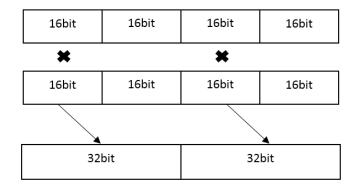

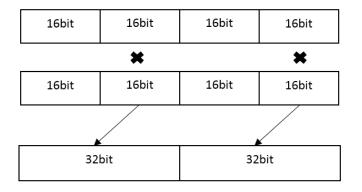

or even indexed subwords as shown in figures 2.11 and 2.12. The two 32bit size products of the multiplication form the new result. The multiplier performs the multiplication instructions, which are the following: Pmul, Pmulshr. Table 2.6 displays the list of the ports used by the multiplier module.

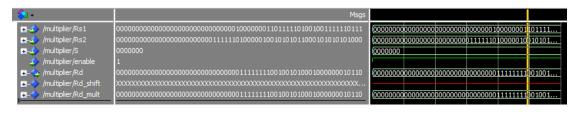

Figure 2.10 displays a simulation of the multiplier. The pmul.odd instruction is executed where the odd indexed subwords (63 donwto 48 and 31 downto 16) of each of the values in Rs1 and Rs2 are multiplied and the two 32 bit results are written to the left and right half word respectively. Since the multiplier does not operate with a clock the maximum frequency is calculated from the maximum propagation delay and is found to be 177,366 MHZ and it takes 1% of the FPGA area.

FIGURE 2.11: Odd indexed multiplication

FIGURE 2.12: Even indexed multiplication

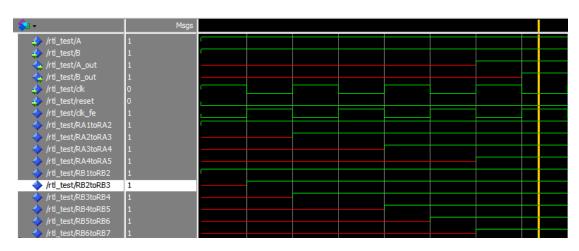

### 2.5.3 The Mix Unit

The Mix Unit is responsible for all the mix and multiplex instructions. It is basically a series of multiplexers and depending on the instruction it receives two inputs and rearranges the subwords accordingly. The mix unit performs the following mixing operations: Mix, Mux, Perm. Table 2.7 displays the list of the ports used by the Mix Unit.

Figure 2.13 displays the simulation of the Mix unit. A mix.l.4 instruction is executed where odd-indexed subwords are selected alternately from Rs1 and Rs2, and written to Rd. The first subword of Rd is the first subword of Rs1. The maximum frequency is found from the propagation delay and is calculated to be 269,759 MHz. The occupied area is 1%.

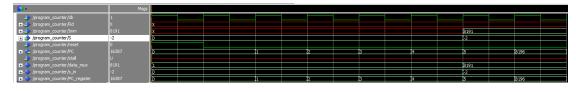

| 🌮 🗧               | Msgs                                           |                                             |

|-------------------|------------------------------------------------|---------------------------------------------|

| 🖃 🅠 /mix_unit/Rs1 | 0 10 10 10 1000 10 10 10 10 10 10 10 10        | 0 10 10 10 10 10 10 10 10 10 10 10 10 10    |

| 🖃 🎝 /mix_unit/Rs2 | 000001111111111111111111111111111111111        | 000001111111111101111111111111111111111     |

| 😐 🌧 /mix_unit/S   | 00011                                          | 00011                                       |

| /mix_unit/enable  | 1                                              |                                             |

| 🔲 🙀 /mix_unit/Rd  | 0 10 10 10 100000 1110 10 10 10 10 111 1110 10 | 0101010100000111010101010111111010100001111 |

| ➡─� /mix_unit/s1  | 0101010100010101                               | 0101010100010101                            |

| ➡→ /mix_unit/s2   | 0101010101011101                               | 0101010101011101                            |

| ➡─� /mix_unit/s3  | 0 10 10 10 10 10 10 10                         | 0101010100101010                            |

|                   | 1010101001111111                               | (101010101111111                            |